| SPEC No | ). C   | C26Z( | 001A |

|---------|--------|-------|------|

| ISSUE   | : Apr. | 14    | 2015 |

| To |  |  |  |

|----|--|--|--|

| 10 |  |  |  |

## **PRELIMINARY**

## **SPECIFICATIONS**

| Product Type | 1/1-type Progressive Scan B/W CCD Area Sensor with 8M Pixels (4ch) |

|--------------|--------------------------------------------------------------------|

| Model No     | RJ3DV4AE0DT                                                        |

\* This specifications contains 24 pages including the cover and appendix. If you have any objections, please contact us before issuing purchasing order.

**CUSTOMERS ACCEPTANCE** DATE: <u>BY:</u>

PRESENTED

J.NAKAI

Dept. General Manager

REVIEWED BY:

PREPARED BY:

T. Yoshida T. Kenzak!

Development Dept.VI Sensing Device Unit Electronic Components And Devices Division SHARP CORPORATION

## **SHARP**

#### RJ3DV4AF0DT

- Handle this document carefully for it contains material protected by international copyright law.

Any reproduction, full or in part, of this material is prohibited without the express written permission of the company.

- When using the products covered herein, please observe the conditions written herein and the precautions outlined in the following paragraphs. In no event shall the company be liable for any damages resulting from failure to strictly adhere to these conditions and precautions.

- (1) Please do verify the validity of this part after assembling it in customer's products, when customer wants to make catalogue and instruction manual based on the specification sheet of this part.

- (2) The products covered herein are designed and manufactured for the following application areas. When using the products covered herein for the equipment listed in Paragraph (3), even for the following application areas, be sure to observe the precautions given in Paragraph (3). Never use the products for the equipment listed in Paragraph (4).

Office electronics

- · Instrumentation and measuring equipment

- Machine tools

- · Audiovisual equipment

- Home appliance

- · Communication equipment other than for trunk lines

- (3) Those contemplating using the products covered herein for the following equipment which demands high reliability, should first contact a sales representative of the company and then accept responsibility for incorporating into the design fail-safe operation, redundancy, and other appropriate measures for ensuring reliability and safety of the equipment and the overall system.

- Control and safety devices for airplanes, trains, automobiles, and other transportation equipment

- Mainframe computers

- Traffic control systems

- · Gas leak detectors and automatic cutoff devices

- · Rescue and security equipment

- · Other safety devices and safety equipment, etc

- (4) Do not use the products covered herein for the following equipment which demands extremely high performance in terms of functionality, reliability, or accuracy.

- · Aerospace equipment

- · Communications equipment for trunk lines

- · Control equipment for the nuclear power industry

- Medical equipment related to life support, etc.

- (5) Please direct all queries and comments regarding the interpretation of the above three Paragraphs to a sales representative of the company.

- O Please direct all queries and regarding the products covered herein to a sales representative of the company.

#### CONTENTS

| 1  | DESCRIPTION 1.1 Features 1.2 Applications                                                                                             | 2  |

|----|---------------------------------------------------------------------------------------------------------------------------------------|----|

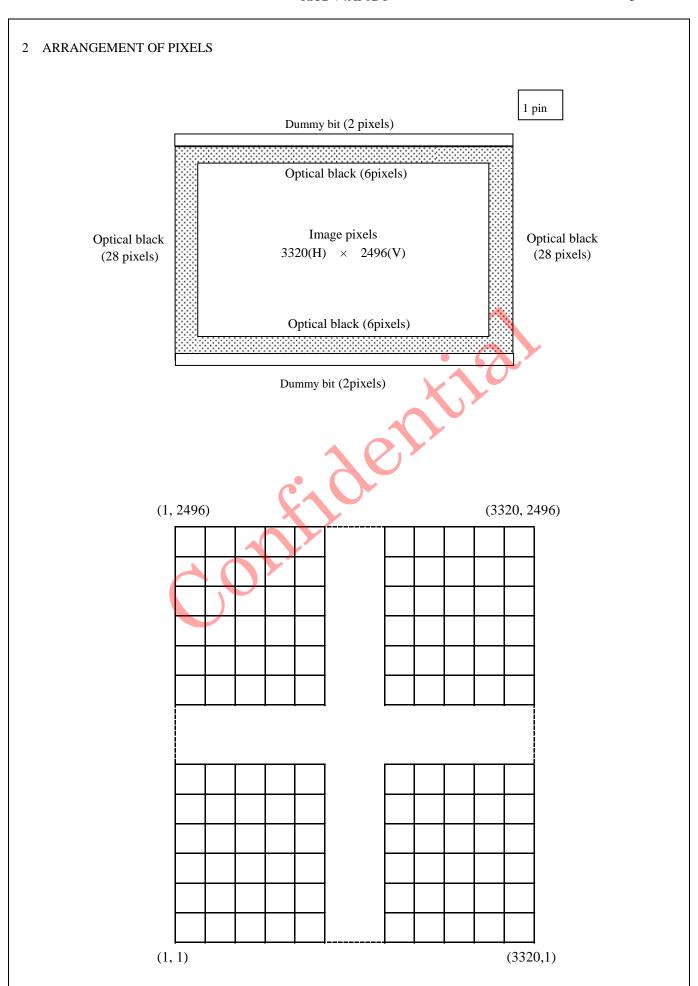

| 2  | ARRANGEMENT OF PIXELS                                                                                                                 | 3  |

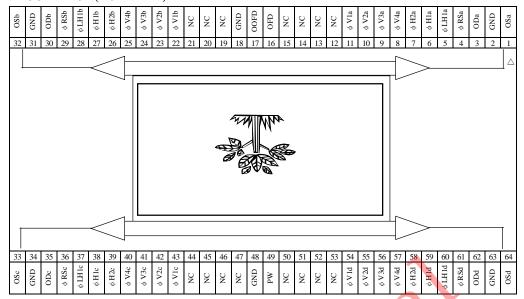

| 3  | PIN CONFIGURATION                                                                                                                     | 4  |

| 4  | ABSOLUTE MAXIMUM RATINGS                                                                                                              | 4  |

| 5  | RECOMMENDED OPERATING CONDITIONS                                                                                                      | 5  |

| 6  | CHARACTERISTICS                                                                                                                       | 6  |

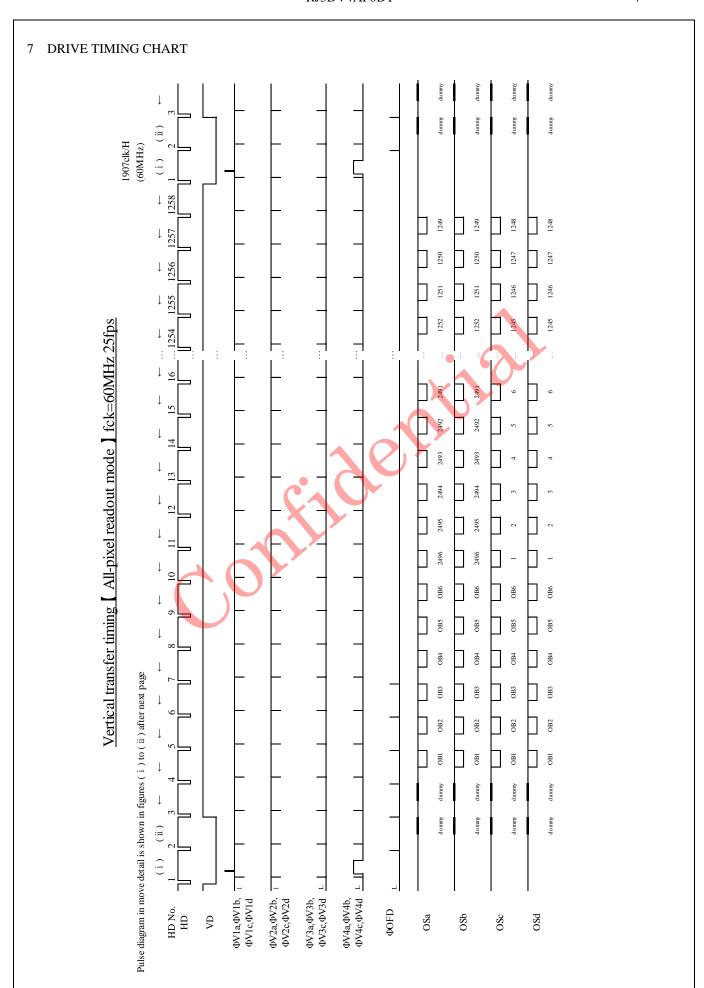

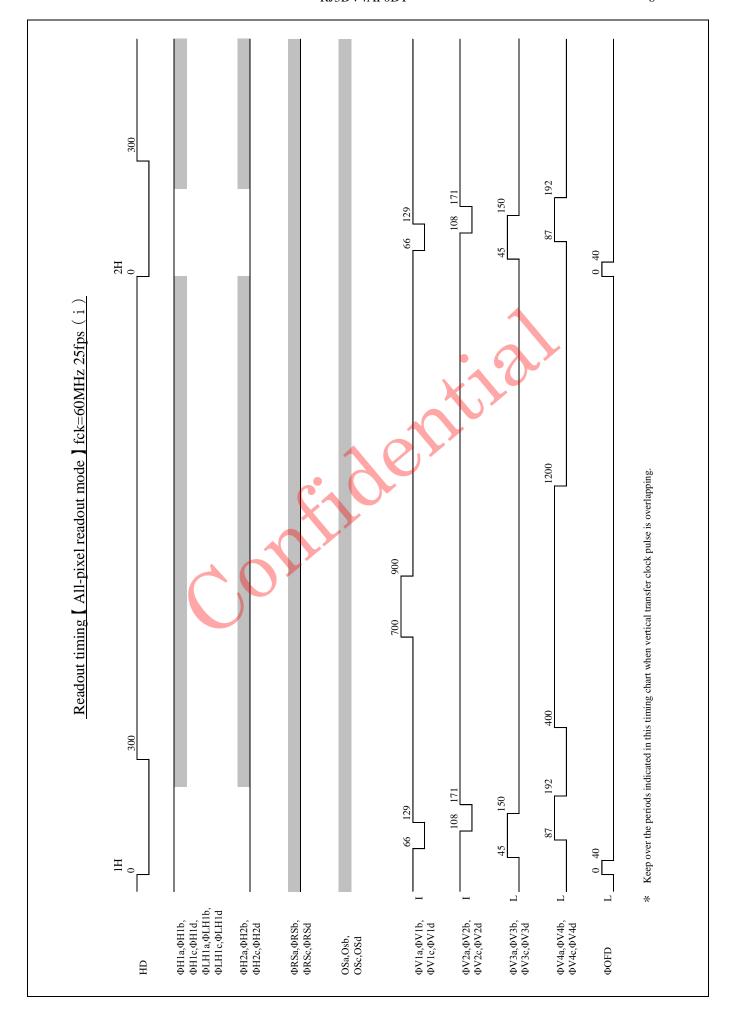

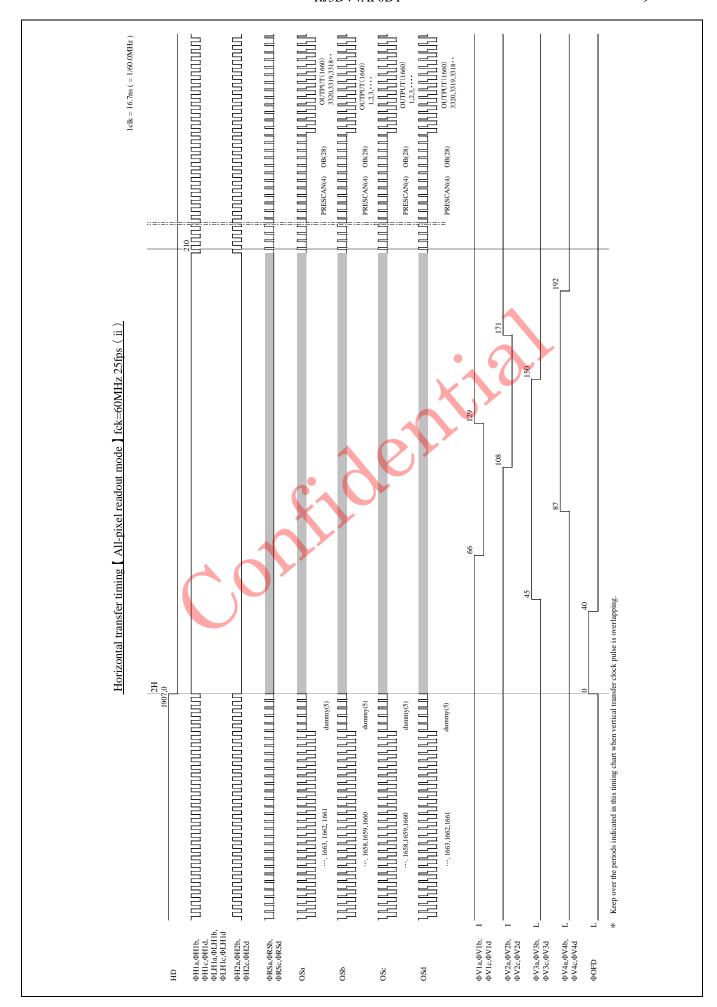

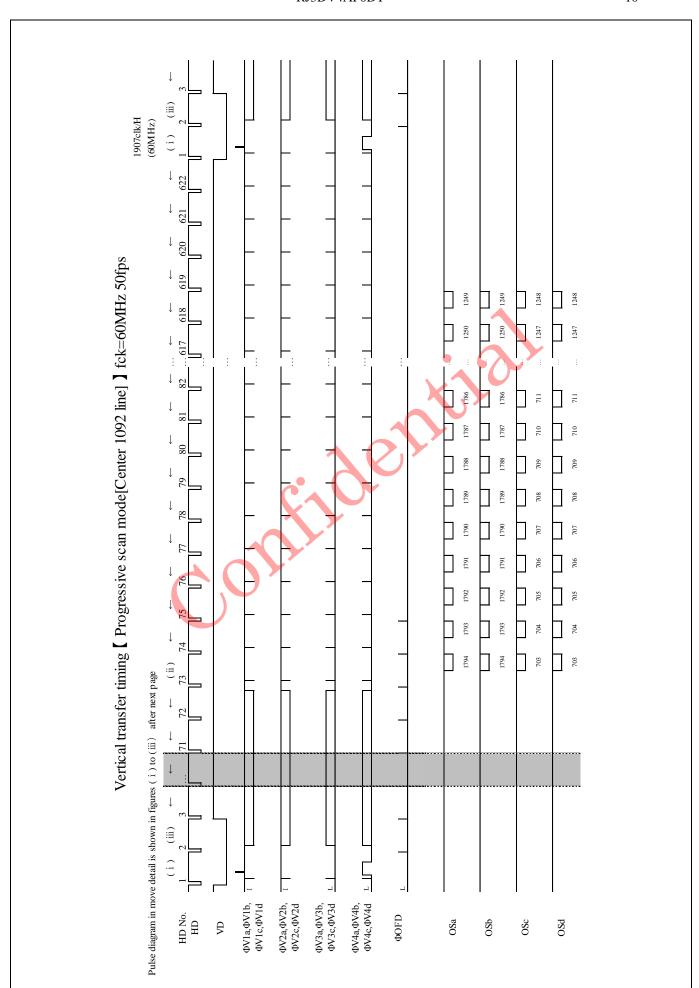

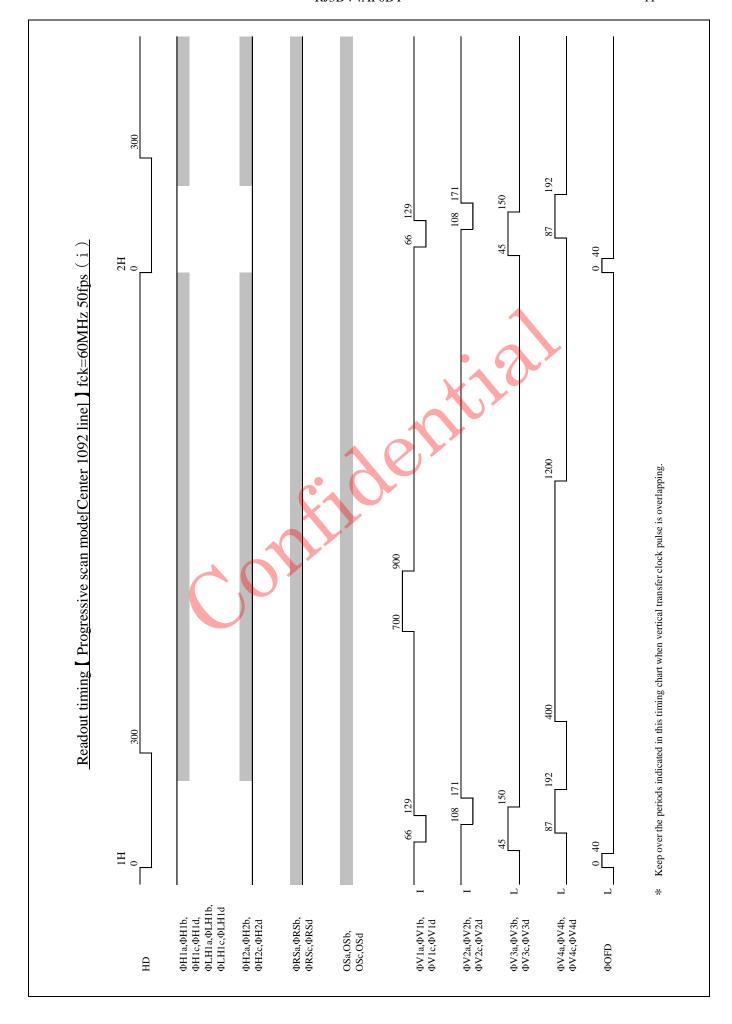

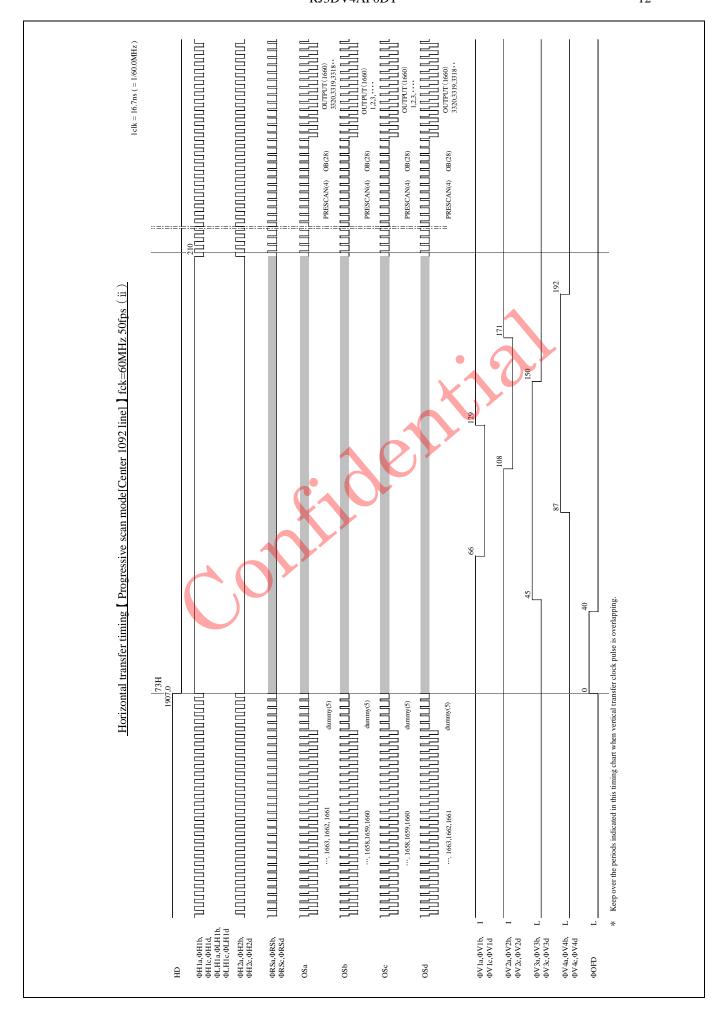

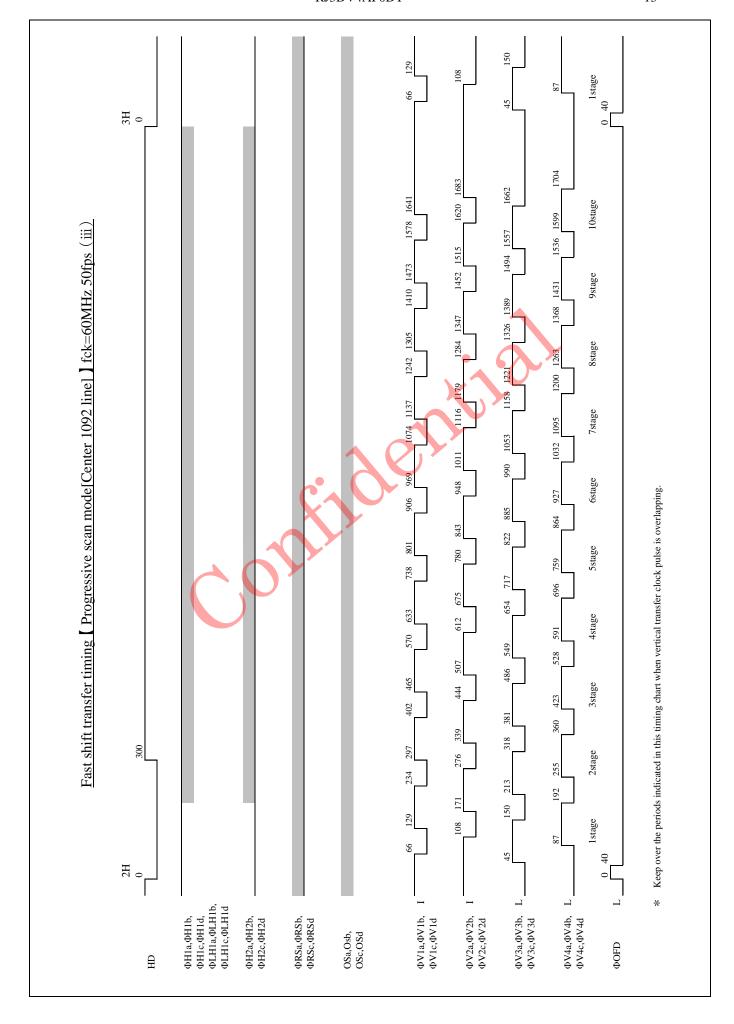

| 7  | DRIVE TIMING CHART                                                                                                                    | 7  |

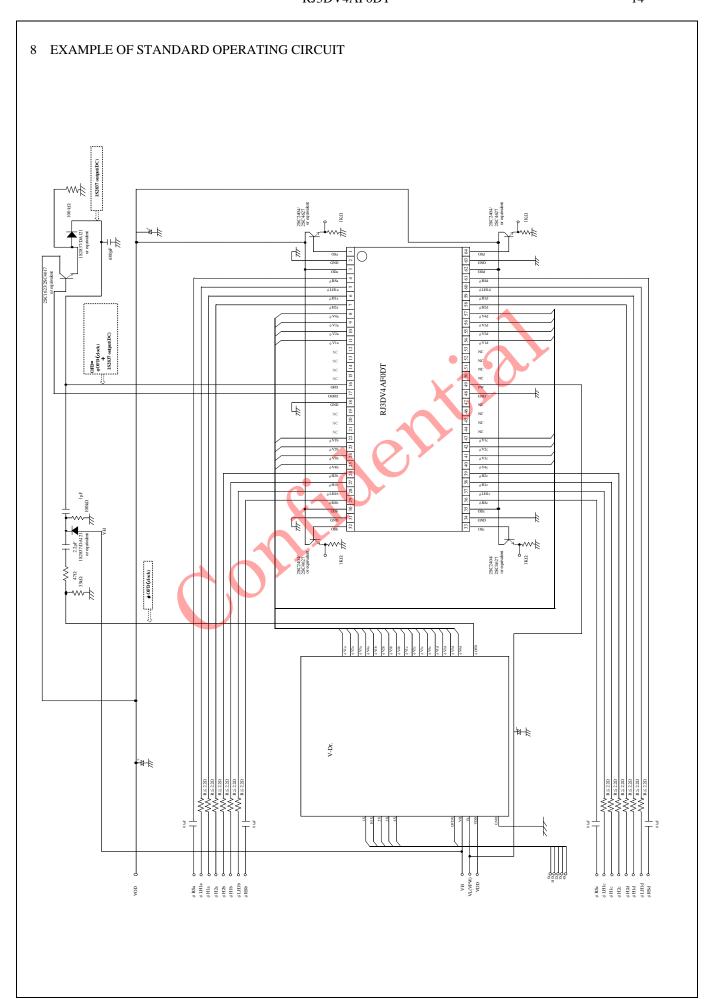

| 8  | EXAMPLE OF STANDARD OPERATING CIRCUIT                                                                                                 | 14 |

| 9  | SPECIFICATION FOR BLEMISH                                                                                                             | 15 |

| 10 | PRECAUTIONS                                                                                                                           | 17 |

|    | <ul> <li>10.1 Package Breakage</li> <li>10.2 Electrostatic Damage</li> <li>10.3 Dust and Contamination</li> <li>10.4 Other</li> </ul> |    |

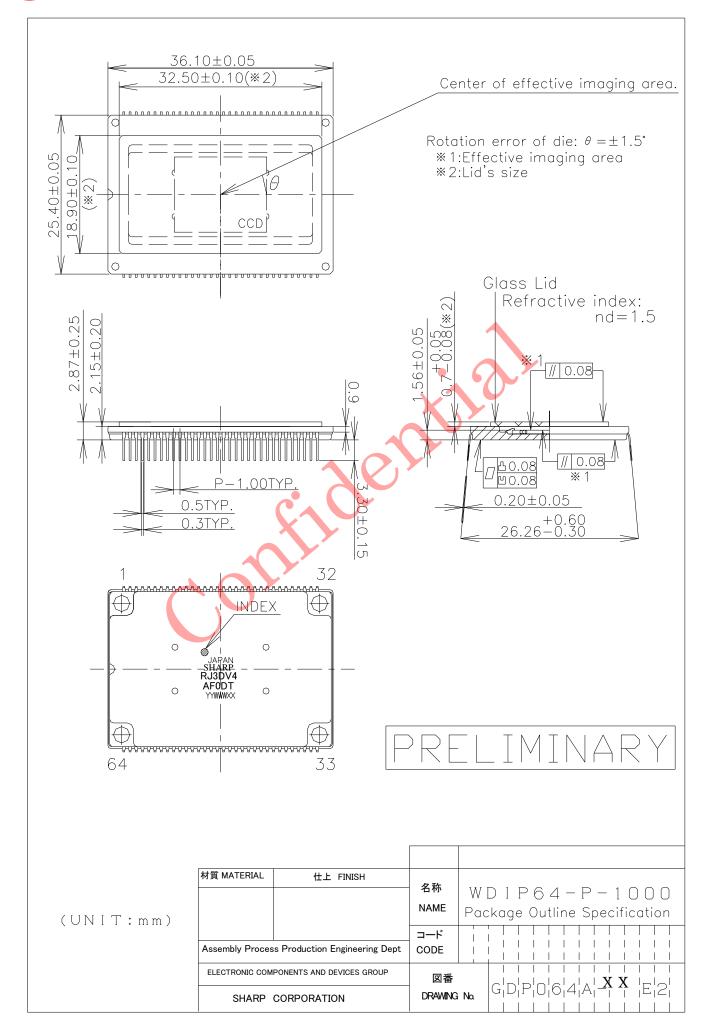

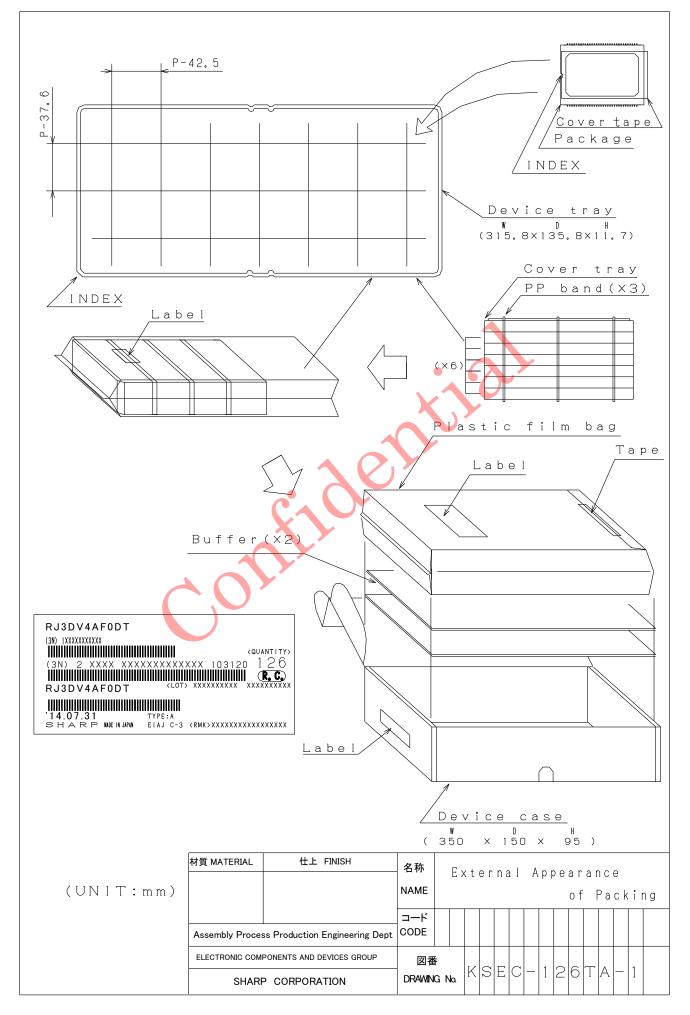

| 11 | PACKAGE OUTLINES AND PACKING SPECIFICATIONS                                                                                           | 19 |

# RJ3DV4AF0DT

1/1-type Progressive Scan B/W CCD Area Sensor with 8M Pixels (4ch)

#### 1 DESCRIPTION

The RJ3DV4AF0DT is a 1/1-type solid-state image sensor that consists of PN photo-diodes and CCDs (charge-coupled devices,4ch). With approximately 8,467k pixels, the sensor provides a high resolution stable B/W image.

1.1 Features

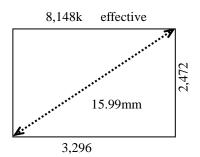

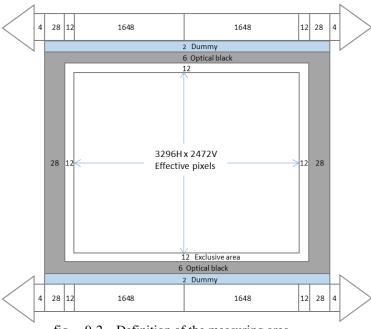

1) Optical size : 15.99 mm (Aspect ratio 4:3)

2) Progressive scan format

3) Square pixel

4) Number of total pixels

Horizontal 3376 × Vertical 2508

Number of image pixels

Horizontal 3320 × Vertical 2496

Number of effective pixels

Horizontal 3296 × Vertical 2472

Pixel pitch : Horizontal 3.88  $\mu$  m × Vertical 3.88  $\mu$  m Number of optical black pixels : Horizontal ; 28 front (per channel)

l black pixels : Horizontal ; 28 front (per channel) : Vertical ; 6 front (per channel)

Number of dummy bits : Horizontal ; 4 front (per channel) : Vertical ; 2 front (per channel)

5) B/W image

- 6) Built-in overflow drain voltage output circuit, and reset gate voltage circuit

- 7) Variable electronic shutter

- 8) Low fixed pattern noise and lag

- 9) No burn-in and no image distortion

- 10) Blooming suppression structure

- 11) Built-in output amplifier

- 12) N-type silicon substrate, N-MOS process, Not designed or rated as radiation hardened

- 13) Global shutter

- 1) Industrial monitor cameras

- 2) Intelligent Transport Systems cameras

- 3) Video capturing devices for PCs, etc

#

"iSHCCD II", "iSHCCD" and "iSHartina" are the trademarks of Sharp Corporation.

The "iSHCCD II" is an advanced CCD image sensor that drastically improves light efficiency by including near-infrared light region as a basic structure of "iSHCCD".

The "iSHartina" series is a key device group of Sharp which realizes a next-generation sensing world.

The circuit diagram and others included in this specifications are intended for use to explain typical application examples. Therefore, we take no responsibility for any problem as may occur due to the use of the included circuit and for any problem with industrial proprietary rights or other rights.

#### 3 PIN CONFIGURATION(TOP VIEW)

| Symbol                                                                                                                                                                                                                                                                 | Pin name                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| ODa,ODb,ODc,ODd                                                                                                                                                                                                                                                        | Output transistor drain                                        |

| OSa,OSb,OSc,OSd                                                                                                                                                                                                                                                        | Output signals                                                 |

| $\phi$ RSa, $\phi$ RSb, $\phi$ RSc, $\phi$ RSd                                                                                                                                                                                                                         | Reset transistor clock                                         |

| <ul> <li>Φ V1a, Φ V1b, Φ V1c, Φ V1d,</li> <li>Φ V2a, Φ V2b, Φ V2c, Φ V2d,</li> <li>Φ V3a, Φ V3b, Φ V3c, Φ V3d,</li> <li>Φ V4a, Φ V4b, Φ V4c, Φ V4d</li> <li>Φ LH1a, Φ LH1b, Φ LH1c, Φ LH1d, Φ H1a, Φ H1b,</li> <li>Φ H1c, Φ H1d, Φ H2a, Φ H2b, Φ H2c, Φ H2d</li> </ul> | Vertical shift register clock  Horizontal shift register clock |

| OFD                                                                                                                                                                                                                                                                    | Overflow drain                                                 |

| OOFD                                                                                                                                                                                                                                                                   | Output overflow drain                                          |

| PW                                                                                                                                                                                                                                                                     | P_well                                                         |

| GND                                                                                                                                                                                                                                                                    | Ground                                                         |

#### 4 ABSOLUTE MAXIMUM RATINGS

$(T_A=25^{\circ}C)$

|                                                      |                             | (-11                     | ,               |

|------------------------------------------------------|-----------------------------|--------------------------|-----------------|

| Parameter                                            | Symbol                      | Ratings                  | Unit            |

| Output transistor drain voltage                      | $V_{\mathrm{OD}}$           | 0 to +15.4               | V               |

| Overflow drain voltage                               | $V_{ m OFD}$                | 0 to +32                 | V               |

| Overflow drain output voltage                        | $V_{OOFD}$                  | Internal output (Note 1) |                 |

| Reset gate clock voltage                             | $V_{\phi RS}$               | Internal output (Note 2) |                 |

| Vertical shift register clock voltage                | $V_{\phi V}$                | V <sub>PW</sub> to +15.4 | V               |

| Horizontal shift register clock voltage              | $V_{\phi H}$                | -0.3 to +5.1             | V               |

| Voltage difference between P_well and vertical clock | $V_{PW}$ - $V_{\phi V}$     | -23.8 to +0              | V               |

| Voltage difference between vertical clocks           | $V_{\phi V}$ - $V_{\phi V}$ | 0 to +9.9 (Note 3)       | V               |

| Storage temperature                                  | $T_{STG}$                   | -40 to +90               | $^{\circ}$ C    |

| Ambient operating temperature                        | $T_{OPR}$                   | -20 to +85               | $_{\mathbb{C}}$ |

- (Note 1) Use the circuit parameter indicated in "8. EXAMPLE OF STANDARD OPERATING CIRCUIT" and do not connect to DC voltage directly. When OOFD is connected to GND, connect V<sub>OD</sub> to GND.

- (Note 2) Do not connect to DC voltage directly. When  $\phi_{RS}$  is connected to GND, connect  $V_{OD}$  to GND. Reset gate clock is applied below 5.1 Vp-p.

- (Note 3) When clock width is below 10  $\,\mu$  s, and clock duty factor is below 0.1 %, voltage difference between adjoining vertical clocks are guaranteed up to 15.4 V. Do not change all  $\phi$  V during 0.5  $\mu$  s before rising edge of V  $_{\phi}$  VH pulse and after falling edge of V  $_{\phi}$  VH pulse.

Do not change directly into  $V_{\phi VL} \rightarrow V_{\phi VH}$  or  $V_{\phi VH} \rightarrow V_{\phi VL}$ .

#### 5 RECOMMENDED OPERATING CONDITIONS

| Parameter                                        |                    | Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Min. | Typ. | Max.          | Unit         |

|--------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|---------------|--------------|

| Ambient operation                                | ng temperature     | $T_{OPR}$                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      | 25.0 |               | $^{\circ}$ C |

| Output transistor                                | drain voltage      | $V_{\mathrm{ODa}}, V_{\mathrm{ODb}}, V_{\mathrm{ODc}}, V_{\mathrm{ODd}}$                                                                                                                                                                                                                                                                                                                                                                                     | 13.1 | 13.5 | 13.9          | V            |

| Overflow drain clock                             | p-p level (Note 1) | $ m V_{\phi OFD}$                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19.3 | 20.0 | 20.7          | V            |

| Ground                                           |                    | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      | 0.0  |               | V            |

| P_well voltage                                   | (Note 2)           | $V_{\mathrm{PW}}$                                                                                                                                                                                                                                                                                                                                                                                                                                            | -6.8 |      | $V_{\phi VL}$ | V            |

| Vertical shift                                   | LOW level          | $V_{\phi V1aL}, V_{\phi V1bL}, V_{\phi V1cL}, V_{\phi V1dL}, \\ V_{\phi V2aL}, V_{\phi V2bL}, V_{\phi V2cL}, V_{\phi V2dL}, \\ V_{\phi V3aL}, V_{\phi V3bL}, V_{\phi V3cL}, V_{\phi V3dL}, \\ V_{\phi V4aL}, V_{\phi V4bL}, V_{\phi V4cL}, V_{\phi V4dL}$                                                                                                                                                                                                    | -6.8 | -6.5 | -6.2          | V            |

| register clock                                   | INTERMEDIATE level | $\begin{array}{c} V_{\phi V1aI,}V_{\phi V1bI,}V_{\phi V1cI,}V_{\phi V1dI,} \\ V_{\phi V2aI,}V_{\phi V2bI,}V_{\phi V2cI,}V_{\phi V2dI,} \\ V_{\phi V3aI,}V_{\phi V3bI,}V_{\phi V3cI,}V_{\phi V3dI,} \\ V_{\phi V4aI,}V_{\phi V4bI,}V_{\phi V4cI,}V_{\phi V4dI} \end{array}$                                                                                                                                                                                   |      | 0.0  |               | V            |

|                                                  | HIGH level         | $V_{\phi V1aH}, V_{\phi V1bH}, V_{\phi V1cH}, V_{\phi V1dH}$                                                                                                                                                                                                                                                                                                                                                                                                 | 13.1 | 13.5 | 13.9          | V            |

| Horizontal shift register clock HIGH level       |                    | $V_{\phi LH1aL}, V_{\phi LH1bL}, \\ V_{\phi LH1cL}, V_{\phi LH1dL}, \\ V_{\phi H1aL}, V_{\phi H1bL}, \\ V_{\phi H1cL}, V_{\phi H1dL}, \\ V_{\phi H2cL}, V_{\phi H2bL}, \\ V_{\phi H2cL}, V_{\phi H2dL} \\ \\ V_{\phi LH1aH}, V_{\phi LH1bH}, \\ V_{\phi LH1cH}, V_{\phi LH1dH}, \\ V_{\phi H1aH}, V_{\phi H1dH}, \\ V_{\phi H1cH}, V_{\phi H1dH}, \\ V_{\phi H1cH}, V_{\phi H1dH}, \\ V_{\phi H2cH}, V_{\phi H2dH} \\ \\ V_{\phi H2cH}, V_{\phi H2dH} \\ \\$ | 3.15 | 0.0  | 3.6           | V            |

| Reset gate clock p-p level (Note 1)              |                    | $V_{\phi RSa,}V_{\phi RSb,} \ V_{\phi RSc,}V_{\phi RSd,}$                                                                                                                                                                                                                                                                                                                                                                                                    | 3.15 |      | 3.6           | V            |

| Vertical shift register clock frequency (Note 3) |                    | $\begin{split} f_{\phi V1a}, & f_{\phi V1b}, f_{\phi V1c}, f_{\phi V1d}, \\ f_{\phi V2a}, & f_{\phi V2b}, f_{\phi V2c}, f_{\phi V2d}, \\ f_{\phi V3a}, & f_{\phi V3b}, f_{\phi V3c}, f_{\phi V3d}, \\ f_{\phi V4a}, & f_{\phi V4b}, f_{\phi V4c}, f_{\phi V4d} \end{split}$                                                                                                                                                                                  |      | 31.5 |               | KHz          |

| Horizontal shift register clock frequency        |                    | f <sub>LH1a</sub> ,f <sub>LH1b</sub> ,f <sub>LH1c</sub> ,f <sub>LH1d</sub> ,<br>f <sub>H1a</sub> ,f <sub>H1b</sub> ,f <sub>H1c</sub> ,f <sub>H1d</sub> ,<br>f <sub>H2a</sub> ,f <sub>H2b</sub> ,f <sub>H2c</sub> ,f <sub>H2d</sub>                                                                                                                                                                                                                           |      | 60.0 |               | MHz          |

| Reset gate clock freque                          | ncy                | $f_{\phi RSa,}f_{\phi RSb,},f_{\phi RSc,}f_{\phi RSd}$                                                                                                                                                                                                                                                                                                                                                                                                       |      | 60.0 |               | MHz          |

- (Note 1) Use the circuit parameter indicated in "8 EXAMPLE OF STANDARD OPERATING CIRCUIT", and do not connect to DC voltage directly.

- (Note 2)  $V_{PW}$  is set below  $V_{\phi VL}$  that is low level of vertical shift register clock, or is used with the same power supply that is connected to  $V_L$  of V driver IC.

- (Note 3) At frame accumulation mode.

- lpha To apply power, first connect GND and then turn on  $V_{OD}$ . After turning on  $V_{OD}$ , turn on  $V_{PW}$  first and then turn on other powers and pulses.

- Do not connect the device to or disconnect it from the plug socket while power is being applied.

SHARP

RJ3DV4AF0DT 6

6 CHARACTERISTICS (Drive method: 1/30s frame accumulation)

$T_A$ : +25°C, but +60°C for parameter No.4 and No.5.

Operating conditions: the typical values specified in "5 RECOMMENDED OPERATING CONDITIONS". Color temperature of light source: 3200K, IR cut-off filter (CM-500,1 mm) is used.

| No. | Parameter                       | Symbol            | Note | Minimum | Typical | Maximum | Unit |

|-----|---------------------------------|-------------------|------|---------|---------|---------|------|

| 1   | Standard output voltage         | $V_{\rm O}$       | 1    |         | 150     |         | mV   |

| 2   | Photo response non-uniformity   | PRNU              | 2    |         |         | 10      | %    |

| 3   | Saturation output voltage       | $V_{SAT}$         | 3    | 700     |         |         | mV   |

| 4   | Dark output voltage             | $V_{DARK}$        | 4    |         | 0.5     | 3.0     | mV   |

| 5   | Dark signal non-uniformity      | DSNU              | 5    |         | 0.5     | 2.0     | mV   |

| 6   | Sensitivity                     | R                 | 6    | 880     | 1100    |         | mV   |

| 7   | Smear ratio                     | SMR               | 7    |         | -120    | -105    | dB   |

| 8   | Image lag                       | AI                | 8    |         |         | 1.0     | %    |

| 9   | Blooming suppression ratio      | ABL               | 9    | 1000    |         |         |      |

| 10  | Output transistor drain current | $I_{\mathrm{OD}}$ |      |         | 24.0    |         | mA   |

#### [ Notes ]

- 1 The average output voltage of signal under the uniform illumination. The standard exposure conditions are defined as when  $V_0$  is 150 mV.

- 2 The image area is divided into  $10 \times 10$  segments under the standard exposure conditions. Each segment's voltage is the average output voltage of all pixels within the segment. PRNU is defined by  $(Vmax-Vmin)/V_0$ , where Vmax and Vmin are the maximum and minimum values of each segment's voltage respectively.

- 3 The image area is divided into  $10 \times 10$  segments. Each segment's voltage is the average output voltages of all pixels within the segment. Vsat is the minimum segment's voltage under 15 times exposure of the standard exposure conditions.

- 4 The average output voltage under non-exposure conditions.

- 5 The image area is divided into 10 × 10 segments under non-exposure conditions. DSNU is defined by (Vdmax Vdmin), where Vdmax and Vdmin are the maximum and minimum values of each segment's voltage respectively.

- 6 The average output voltage of signal when a 1000 lux light source with a 90 % reflector is imaged by a lens of F4, f50 mm.

- The sensor is exposed only in the central area of V/10 square with a lens at F4, where V is the vertical image size. SMR is defined by the ratio of the output voltage detected during the vertical blanking period to the maximum output voltage in the V/10 square.

- 8 The sensor is exposed at the exposure level corresponding to the standard conditions. AI is defined by the ratio of the output voltage measured at the 1st field during the non-exposure period to the standard output voltage.

- 9 The sensor is exposed only in the central area of V/10 square, where V is the vertical image size. ABL is defined by the ratio of the exposure at the standard conditions to the exposure at a point where blooming is observed.

#### [ Comment ]

Within the recommended operating conditions of VoD, VoFD of the internal output satisfies with ABL and VSAT.

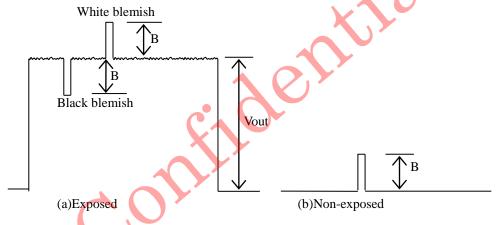

#### 9 SPECIFICATION FOR BLEMISH (1/30 s frame accumulation)

#### 1) Definition of blemish

|                | Level | of     | blem | ish (1 | mV) | Permitted number of blemish | Comment                    |

|----------------|-------|--------|------|--------|-----|-----------------------------|----------------------------|

| White blemish  | 100   | $\leq$ | В    |        |     | 1                           | • See fig.9-1(a), fig.9-2. |

| (Exposed)      |       |        | В    | <      | 100 | no count                    | $\cdot$ Vout = Vstd        |

|                | 120   | $\leq$ | В    |        |     | 1                           |                            |

| Black blemish  | 55    | $\leq$ | В    | <      | 120 | 15                          |                            |

| (Exposed)      | 40    | $\leq$ | В    | <      | 55  | 15                          |                            |

|                |       |        | В    |        | 40  | no count                    |                            |

|                | 100   | <      | В    |        |     | 1                           | • See fig.9-1(b), fig.9-2  |

| White blemish  | 20    | <      | В    | $\leq$ | 100 | N                           | • N≦150                    |

| (Non-Exposed)  | 2.5   | <      | В    | $\leq$ | 20  | M                           | $\cdot$ M+N $\leq$ 750     |

|                |       |        | В    | $\leq$ | 2.5 | no count                    | Ay                         |

| White blemish  | 5.0   | $\leq$ | В    |        |     | 0                           | • See fig.9-1(a), fig.9-2. |

| (Shutter mode) |       |        | В    | <      | 5.0 | no count                    | Vout = Vstd/10             |

| Black blemish  | 5.0   | $\leq$ | В    |        |     | 0                           | • The electronic shutter   |

| (Shutter mode) |       |        | В    | <      | 5.0 | no count                    | speed is set at 1/10000 s  |

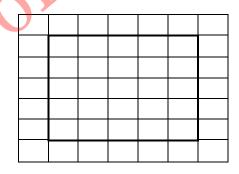

\* Total number of white blemish (non-exposed:20 < B) and black blemish (exposed:55 ≤ B) are less than 2 in arbitrary 5×5 pixels areas.

ex. The defects are less than 2 in the subsequent area surrounded by bold lines.

· Vout : Average output voltage

• Vstd : 150 mV (The average output voltage). The standard

output voltage defined in the specification of the characteristics.

16

#### [MEASURING CONDITION]

• Ta: 60 ℃

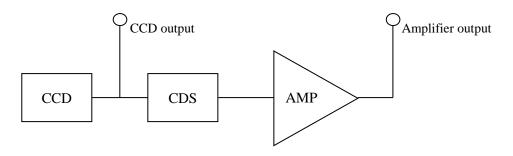

· Measuring block diagram

The output voltage is measured at the CCD output.

The gain of the amplifier is adjusted to the unity between the CCD output and the amplifier output.

fig. 9-1 Definition of blemish level

(The wave form is the luminance signal measured at the Amplifier output)

#### [MEASURING AREA]

fig. 9-2 Definition of the measuring area

RJ3DV4AF0DT 17

#### 10 PRECAUTIONS

SHARP

#### 10.1 Package Breakage

In order to prevent the package from being broken, observe the following instructions:

- The CCD is a precise optical component and the package material is plastic. Therefore,

- Take care not to drop the device when mounting, handling, or transporting.

- · Avoid giving a shock to the package. Especially when leads are fixed to the socket or the circuit board, small shock could break the package more easily than when the package isn't fixed.

- 2) When mounting the package on the housing, be sure that the package is not bent.

- If a bent package is forced into place between a hard plate or the like, the package may be broken.

- 3) If any damage or breakage occurs on the surface of the glass cap, its characteristics could deteriorate. Therefore,

- Do not hit the glass cap.

- Do not give a shock large enough to cause distortion.

- Do not scrub or scratch the glass surface.

- Even a soft cloth or applicator, if dry, could cause flaws to scratch the glass.

#### 10.2 Electrostatic Damage

As compared with general MOS-LSI, CCD has lower ESD.

Therefore, take the following antistatic measures when handling the CCD:

- 1) Always discharge static electricity by grounding the human body and the instrument to be used. To ground the human body, provide resistance of about 1 M $\Omega$  between the human body and the ground to be on the safe side.

- 2) When directly handling the device with the fingers, hold the part without leads and do not touch any lead.

- 3) To avoid generating static electricity,

- a. do not scrub the glass surface with cloth or plastic

- b. do not attach any tape or labels

- c. do not clean the glass surface with dust-cleaning tape

- 4) When storing or transporting the device, put it in a container of conductive material.

RJ3DV4AF0DT 18

#### 10.3 Dust and Contamination

SHARP

Dust or contamination on the glass surface could deteriorate the output characteristics or cause a scar. In order to minimize dust or contamination on the glass surface, take the following precautions:

- Handle the CCD in a clean environment such as a cleaned booth. (The cleanliness level should be, if possible, class 1,000 at least.)

- Do not touch the glass surface with the fingers. If dust or contamination gets on the glass surface, the following cleaning method is recommended:

- Dust from static electricity should be blown off with an ionized air blower. For anti-electrostatic measures, however, ground all the leads on the device before blowing off the dust.

- The contamination on the glass surface should be wiped off with a clean applicator soaked in Isopropyl alcohol. Wipe slowly and gently in one direction only.

- Frequently replace the applicator and do not use the same applicator to clean more than one device.

- Note: In most cases, dust and contamination are unavoidable, even before the device is first used. It is, therefore, recommend that the above procedures should be taken to wipe out dust and contamination before using the device.

#### 10.4 Other

- Soldering should be manually performed within 5 seconds at 350°C maximum at the tip of soldering iron.

- 2) Avoid using or storing the CCD at high temperature or high humidity as it is a precise optical component. Do not give a mechanical shock to the CCD.

- 3) CCD has the possibility that white blemish, which originates in the structure of CCD with the passage of time by an external factor such as the radiations, could be generated. Please use white blemish compensation circuit for white blemish generated afterward.

#### 11. PACKAGE OUTLINE AND PACKING SPECIFICATION

#### 1. Package Outline Specification

Refer to attached drawing.

(The seal resin stick out from the package shall be passed.)

#### 2. Markings

Marking contents

(1). Product name : RJ3DV4AF0DT

(2). Company name : SHARP

(3). Country of origin : JAPAN

: <u>YY WW X XX</u> (4). Date code Denotes the production ref.code. $(1 \sim 2 \text{ figures})$ Denotes the production day of the week. 1 2 3 4 5 6 7 MON. TUE. SUN. WED. THU. FRI. SAT. Denotes the production week.  $(01,02,03,\cdots,52,53)$ Denotes the production year.

(Lower two digits of the year.)

Positions of markings are shown in the package outline drawing. But,markings shown in that drawing are not provided any measurements of their characters and their positions.

#### 3. Packing Specification

#### 3-1. Packing materials

| Material Name    | Material Spec.                 | Purpose                                     |  |  |

|------------------|--------------------------------|---------------------------------------------|--|--|

| Cover Tape       | Plastic film(1device/tape)     | Glass lid covering                          |  |  |

| Device case      | Cardboard(126devices/case)     | Device tray fixing                          |  |  |

| Device tray      | Conductive plastic             | Device packing(6trays/case)                 |  |  |

|                  | (21devices/tray)               |                                             |  |  |

| Cover tray       | Conductive plastic(1tray/case) | Device packing                              |  |  |

| PP band          | Polypropylene                  | Device tray fixing                          |  |  |

| Buffer           | Cardboard(2sheets/case)        | Shock absorber of device tray               |  |  |

| Plastic film bag | Plastic film                   | Device tray fixing                          |  |  |

| Tape Paper       |                                | Sealing plastic film bag and device case    |  |  |

| Label            | Paper                          | Indicates part number, quantity and date of |  |  |

|                  |                                | manufacture                                 |  |  |

### 3−2. External appearance of packing

Refer to attached drawing

#### 4. Precaution

- 1). Before unpacking, confirm the imports of the chapter "Handling Precaution" in this device specification.

- 2). Unpacking should be done on the stand treated with anti-ESD. At that time, the same anti-ESD treatment should be done to operator's body, too.

| ISSUE NUMBER |

|--------------|

| 47162ADC     |

Chemical substance information in the product

Product Information Notification based on Chinese law, Management Methods for Controlling

Pollution by Electronic Information Products.

Names and Contents of the Toxic and Hazardous Substances or Elements in the Product

| Lead<br>(Pb) | Mercury<br>(Hg) | Cadmium<br>(Cd) | Hexavalent<br>Chromium<br>(Cr(VI)) | Polybrominated<br>Bophenyls<br>(PBB) | Polybrominated Diphenyl Ethers (PBDE) |

|--------------|-----------------|-----------------|------------------------------------|--------------------------------------|---------------------------------------|

| 0            | 0               | 0               | 0                                  | 0                                    | 0                                     |

- $\circ$ : indicates that the content of the toxic and hazardous substance in all the homogeneous materials of the part is below the concentration limit requirement as described in SJ/T 11363-2006

- ×: indicates that the content of the toxic and hazardous substance in at least one homogeneous material of the part exceeds the concentration limit requirement as described in SJ/T 11363-2006 standard.

ISSUE NUMBER

47162ADC